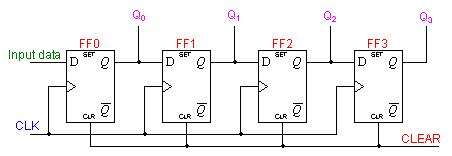

This shift register is configured to shift data from the left to the right.ĭata is fed into the D input of the first flip-flop on the left. This is a four bit shift register and therefore consists of four D flip-flops.

Shift registers consist of D flip-flops as shown in the figure below. A shift register has the capability of shifting the data stored in the register from left to right or right to left. Shift Register Operation A register stores data i.e. Two different ways to code a shift register in VHDL are shown. Finished Pokemon Gba Hacks Download more.

A shift register is written in VHDL and implemented on a Xilinx CPLD. Parvathi Parameshwara Kannada Serial Actress Real Names here. ALL use IEEE.STD_LOGIC_ARIT H.ALL use IEEE.STD_LOGIC_UNSIGNED.A LL entity siso is Port ( sin,clk,rst: in STD_LOGIC q: inout std_logic_vector(2 downto 0) sout: out STD_LOGIC) end siso architecture Behavioral of siso is COMPONENT DFF PORT (data,clock,rst:in std_logic output:out std_logic) end component begin d0: dff port map(sin,clk,rst,q(0)) d1: dff port map(q(0),clk,rst,q(1)) d2: dff port map(q(1),clk,rst,q(2)) d3: dff port map(q(2),clk,rst,sout) end Behavioral.

0 kommentar(er)

0 kommentar(er)